| Design Space Exploration : Architecture |      |      |  |      |                                      |        |        |  |

|-----------------------------------------|------|------|--|------|--------------------------------------|--------|--------|--|

| Feature                                 | P #1 | P #2 |  | P #N | NOC Feature                          | NOC #1 | NOC #m |  |

| I Cache<br>(size, org.)                 |      |      |  |      | Switch<br>architecture               |        |        |  |

| D Cache<br>(size, org.)                 |      |      |  |      | Arbitration<br>Buffers               |        |        |  |

| Local Mem                               |      |      |  |      | Topology<br>Regular<br>heterogeneous |        |        |  |

| FU integer                              |      |      |  |      | Clock domains                        |        |        |  |

| FU FP                                   |      |      |  |      | islands                              |        |        |  |

| HW<br>Accelerators<br>(connection       |      |      |  |      | Flow control                         |        |        |  |

| mode)                                   |      |      |  |      |                                      |        |        |  |

| Internal core                           |      |      |  |      | routing                              |        |        |  |

| Width, pipeline                         |      |      |  |      |                                      |        |        |  |

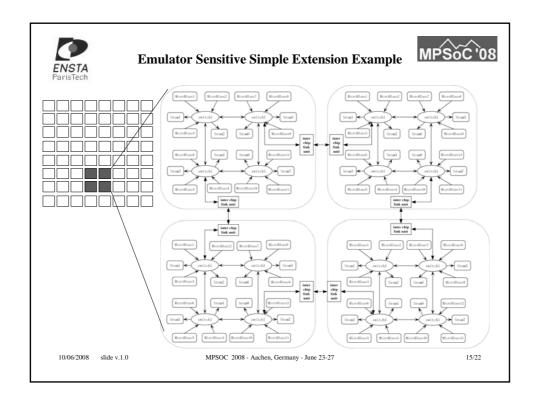

| ParisTech                 | Sranl switchl                                                    | Nicro8laze2      | VicroBlaze?<br>svitchi<br>Srunfi<br>Srunfi | HicroBlace<br>HicroBlace |                   |           |

|---------------------------|------------------------------------------------------------------|------------------|--------------------------------------------|--------------------------|-------------------|-----------|

|                           | Sram3 switchl                                                    | <                | switchi                                    | Sram7                    |                   |           |

| IP component              |                                                                  | licroBlazed      | WicroBlazel0                               | Sram7<br>Micro8laze11    | version           | Qty       |

| IP component<br>Processor | MicroBlaze5 M                                                    | ticroBlaze1      | WicroBlaze10                               | Micro81aze11             | version<br>5.00 b | Qty<br>12 |

| •                         | MicroBlaze5 M<br>description                                     | AicroBlazed      | MicroBlaze10<br>source                     | NicroBlazell             |                   |           |

| Processor                 | WicreBlaze5         W           description         Soft core IP | 4<br>IteroBlazel | MicroBlaze10<br>source<br>Microblaze Soft  | NicroBlazell             | 5.00 b            | 12        |

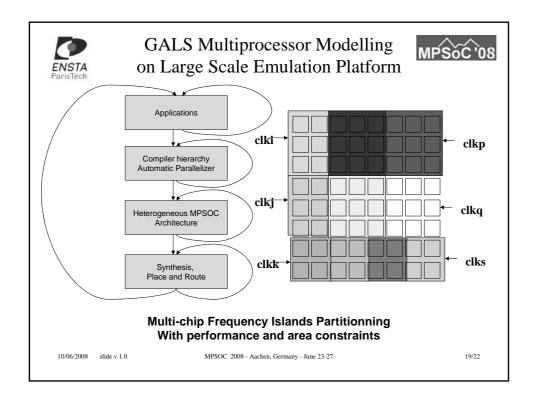

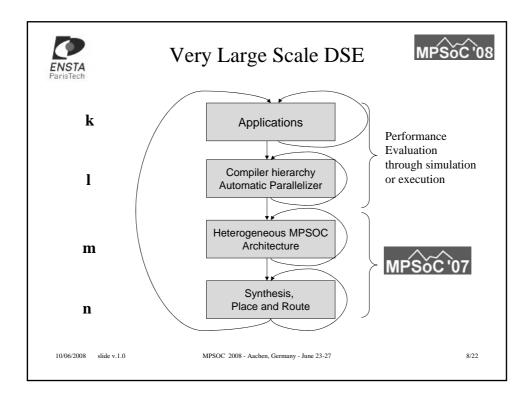

| <ul> <li>Chip multiprocessor may wor<br/>components (processor, netw)</li> <li>Heterogeneous multiprocessor</li> <li>VLS-DSE exploit frequency in</li> </ul> | rk with<br>ork on<br>ors have | multipl<br>chip, m<br>e natura | le clock<br>lemory<br>1 multij | s doma           | ains for<br>ler) | various         |          | ectural |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------|--------------------------------|------------------|------------------|-----------------|----------|---------|------|

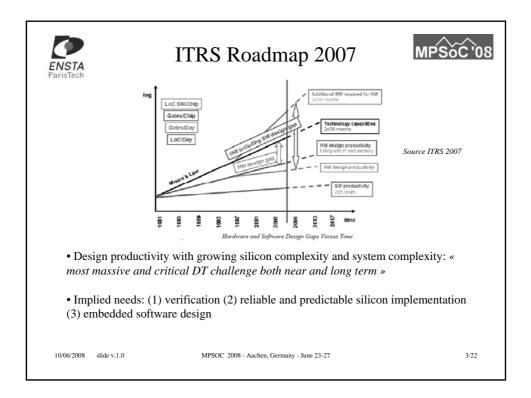

| Logical/Circ                                                                                                                                                 | uit/Phys                      | ical Des                       | ign Tech<br>2009               | nology .<br>2010 | Require<br>2011  | nents—1<br>2012 | Vear-ter | m Years | 2015 |

| 1 ear of Production<br>Asynchronous global signaling:                                                                                                        |                               | 11%                            | 15%                            | 17%              | 19%              | 2012            | 2013     |         | 2015 |

| % of a design driven by handshake clocking                                                                                                                   | 7%                            |                                |                                |                  |                  |                 |          | 23%     |      |

| Parameter uncertainty:%-effect (on signoff delay)                                                                                                            | 6%                            | 8%                             | 10%                            | 11%              | 11%              | 12%             | 14%      | 15%     | 18%  |

| Simultaneous analysis objectives:<br># of objectives during optimization                                                                                     | 4                             | 5                              | 6                              | 6                | 6                | 6               | 7        | 8       | 8    |

| Circuit families: # of families in a single design                                                                                                           | 3                             | 3                              | 4                              | 4                | 4                | 4               | 4        | 4       | 4    |

| Synthesized analog content: % of total design<br>analog content                                                                                              | 15%                           | 16%                            | 17%                            | 18%              | 19%              | 20%             | 23%      | 25%     | 28%  |

| Full-chip leakage (normalized to full-chip leakage<br>power dissipation in 2007)                                                                             | 1                             | 1.5                            | 2                              | 2.5              | 2.75             | 3               | 3.5      | 4       | 6    |

|                                                                                                                                                              |                               |                                |                                |                  |                  |                 | Source   | ITRS 2  | 007  |